2022年《计算机硬件技术基础》试题末考题A答案 .pdf

2022年《计算机硬件技术基础》试题末考题A答案 .pdf

( 4.5 )

( 4.5 )《2022年《计算机硬件技术基础》试题末考题A答案 .pdf》由会员分享,可在线阅读,更多相关《2022年《计算机硬件技术基础》试题末考题A答案 .pdf(6页珍藏版)》请在淘文阁 - 分享文档赚钱的网站上搜索。

1、清华大学本科生考试试题(A)参考答案考试课程计算机硬件技术基础2005 年 6 月 1 3 日班级:姓名:学号:成绩:一二三四五总分请注意共有五道大题一、选择和填空题 (20 分,2分/ 空) 1. 8088系统中断向量表的物理地址范围是00000003FFH2. 若 8255A 的 A口输入, B、C口输出,工作在方式0,则方式控制字为90H 3. 判断两个数是否相等,可以用PSW 中的 ZF 标志及相应指令实现。4. 在 A/D 转换过程中模拟信号有明显变化的场合, A/D 转换的模拟信号输入端应加接采样保持电路。5. PC/XT 总线提供给I/O 操作的控制信号线有 /IOR 、/IOW

2、 6. 可编程接口芯片中与数据总线相连接的电路,应该是一个具有三态门输出功能的电路。7. 8088CPU 中对可屏蔽中断请求的屏蔽控制由 IF 标志实现。8. CPU 上电复位后执行的第一条指令的地址是_FFFF0H9.一片 256kB的 SRAM 芯片,有18 根地址线。10. 若 8250UART的控制字被设置为8FH,则一帧的时间长度为10 ms。二、问答题( 25 分,5 分/ 小题) 。1你认为掌握时序概念有何重要意义?有助于理解计算机的工作原理;有助于时序配合设计;有助于硬件调试。2输出到数据总线的电路都应是可控的三态门电路(或类似功能的电路),为什么?否则将导致数据总线冲突,使计

3、算机不能正常工作3为什么说在应用系统设计中需求分析很重要?通过需求分析可以明确用户需求,明确设计目标,这样才能设计出用户所需要的系统,否则将导致不必要的纠纷。4请说明如何使用DEBUG 命令初步检查实验箱中8255A 及其连线有无错误。用 O命令设置 8255A 的方式控制字,用O和 I 命令对 8255A 进行输出和输入操作,若操作结果正确,则8255A 及其连线正确,否则有可能存在硬件错误。5请说明N号可屏蔽中断从INTR 变高到开始执行相应中断服务子程序的过程。8088CPU的 INTR引脚变高, 若此时满足可屏蔽中断响应条件,则 8088CPU将送出中断响应时序,并从数据总线上获取中断

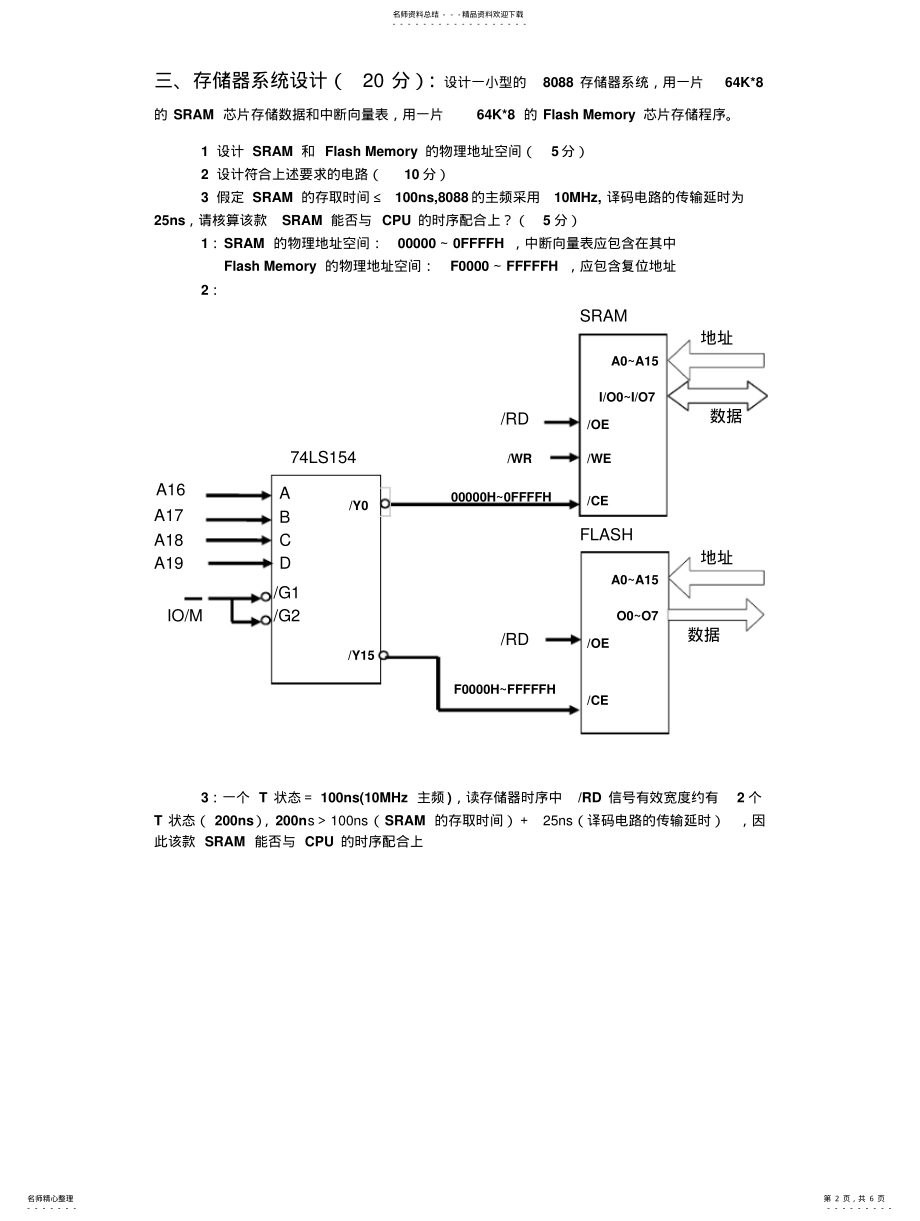

4、类型号N,根据该类型号,8088CPU从中断向量表中获得中断服务子程序的入口地址,并转去执行之。第 1 页/共 2 页五道大题名师资料总结 - - -精品资料欢迎下载 - - - - - - - - - - - - - - - - - - 名师精心整理 - - - - - - - 第 1 页,共 6 页 - - - - - - - - - 三、存储器系统设计(20 分) :设计一小型的8088 存储器系统,用一片64K*8的 SRAM 芯片存储数据和中断向量表,用一片64K*8 的 Flash Memory 芯片存储程序。1 设计 SRAM 和 Flash Memory 的物理地址空间(5分)

5、2 设计符合上述要求的电路(10 分)3 假定 SRAM 的存取时间 100ns,8088的主频采用10MHz, 译码电路的传输延时为25ns,请核算该款SRAM 能否与 CPU 的时序配合上?(5 分)1:SRAM 的物理地址空间:000000FFFFH ,中断向量表应包含在其中Flash Memory 的物理地址空间:F0000FFFFFH ,应包含复位地址2:3:一个 T 状态 100ns(10MHz 主频 ),读存储器时序中/RD 信号有效宽度约有2 个T 状态( 200ns) ,200ns100ns(SRAM 的存取时间)25ns(译码电路的传输延时),因此该款 SRAM 能否与 C

6、PU 的时序配合上/RD地址数据SRAMA0A15 I/O0I/O7 /OE /RD地址数据FLASHA0A15 O0O7 /CE /OE 74LS154ABC/G1/G2A16A17A18IO/MDA19/Y0 /Y15 F0000HFFFFFH 00000H0FFFFH /WE /WR /CE 名师资料总结 - - -精品资料欢迎下载 - - - - - - - - - - - - - - - - - - 名师精心整理 - - - - - - - 第 2 页,共 6 页 - - - - - - - - - 四、信号发生器硬件电路设计(10分) :欲利用 DAC0832 和 PC/XT 总线

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 计算机硬件技术基础 2022年计算机硬件技术基础试题末考题A答案 2022 计算机硬件 技术 基础 试题 考题 答案

淘文阁 - 分享文档赚钱的网站所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

淘文阁 - 分享文档赚钱的网站所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

限制150内